#### SIGNAL INTEGRITY HIGH-SPEED INTERFACE TESTING LANDSCAPE

Bryant Hsu Product Manager Business Development and Marketing Dept.

#### **ROHDE&SCHWARZ**

Make ideas real

## AGENDA

- Application Overview

- ► VNA Based S-Parameter for Signal Integrity Analysis

- High-Speed Interface Challenges and Test Requirements

- Accurate Measurement with Probes or Test Fixture

Conclusions

#### **APPLICATION OVERVIEW**

# HIGH SPEED DIGITAL INTERFACES EXAMPLE

- ► USB <u>U</u>niversal <u>S</u>erial <u>B</u>us

- USB4 Gen2 (20 Gbps), Gen3 (40 Gbps)

- USB3.2 Gen1 (5 Gbps), Gen2 (10 Gbps), Gen2x2 (20 Gbps)

- PCIe <u>Peripheral Computer Interconnect Express</u>

PCIe Gen4 (16 Gbps), Gen5 (32 Gbps), Gen6 (64 Gbps)

- (Q/O)SFP(-DD) (Quad/Octal) Small Form-factor Pluggable

400/800 GbE using PAM-4

Picture reference: wikipedia

COMPANY RESTRICTED

Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

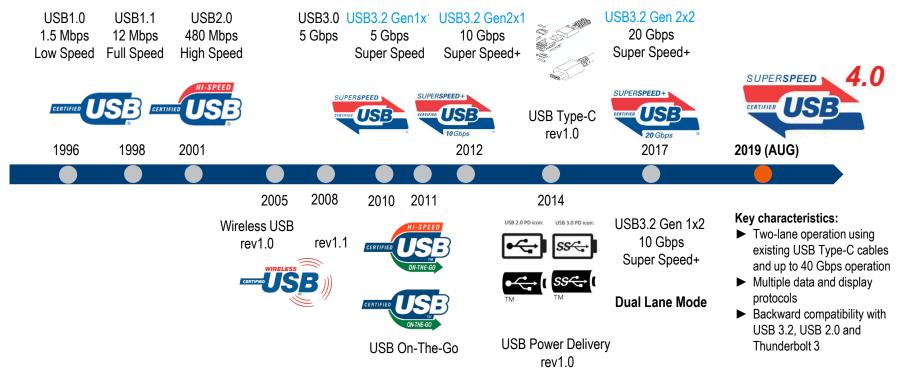

# **USB EVOLUTION**

# **PCI EXPRESS (PCIe)**

- Introduced in 2004

- Peripheral Component Interconnect Express is the de facto standard to connect high performance IO devices to the rest of the system. Eg.NICs, NVMe, graphics, TPUs

- Computer to Peripheral Communication

- Overseen by PCI-SIG

- Full-duplex bidirectional

- Backwards compatibility

Rohde & Schwarz 3/15/2022

|                                                                    | mannoutic      | 711              |               |                 |                                      |  |  |  |

|--------------------------------------------------------------------|----------------|------------------|---------------|-----------------|--------------------------------------|--|--|--|

|                                                                    | Generat<br>ion | Transfer<br>Rate | Total x 16 BW | Coding          | VNA required, GHz<br>(for Interface) |  |  |  |

|                                                                    | PCle 1.x       | 2.5 GT/s         | 4 GB/s        | 8b/10b          | ZNB8                                 |  |  |  |

|                                                                    | PCIe 2.x       | 5.0 GT/s         | 8 GB/s        | 8b/10b          | ZNB8                                 |  |  |  |

|                                                                    | PCIe 3.x       | 8.0 GT/s         | ~ 16 GB/s     | 128b/130b       | ZNB20                                |  |  |  |

|                                                                    | PCIe 4.x       | 16.0 GT/s        | ~ 32 GB/s     | 128b/130b       | ZNB20                                |  |  |  |

|                                                                    | PCIe 5.x       | 32.0 GT/s        | ~ 64 GB/s     | 128b/130b       | ZNB40                                |  |  |  |

|                                                                    | PCle 6.x       | 64.0 GT/s        | ~ 128 GB/s    | 128b/130b (PAM) | ZNB40<br>(spec. in progress)         |  |  |  |

| Signal Integrity for High Speed Interface Testing COMPANY RESTRICT |                |                  |               |                 |                                      |  |  |  |

# **HIGH SPEED ETHERNET INTERFACE**

| IEEE spec. | Infiniband | Form factor                                                 | Baud rate,<br>GBd | Code rate        | Data Rate, Gbps<br>(per lane) | VNA requirement, GHz        |

|------------|------------|-------------------------------------------------------------|-------------------|------------------|-------------------------------|-----------------------------|

| 802.3bj    | EDR        | SFP28<br>QSFP28                                             | 25.78125          | 64b/66b,<br>NRZ  | 25                            | 25                          |

| 802.3cd    | HDR        | SFP56<br>SFP-DD-100G<br>QSFP56<br>QSFP-DD-400G<br>OSFP-400G | 26.5625           | 64b/66b,<br>PAM4 | 50                            | 26.565                      |

| 802.3ck    | NDR        | SFP112<br>SFP-DD112<br>QSFP112<br>QSFP-DD-800G<br>OSFP-800G | 53.125            | 64b/66b,<br>PAM4 | 100                           | 40~50<br>(spec in progress) |

#### **HIGH SPEED INTERFACE CHAIN FOR MOTHERBOARD**

#### PCB material manufacture

- Glass fiber / Fiberglass cloth

- Copper foil

- PI / Resin

#### PCB manufacture

- Copper foil substrate

- PCB /FPC

- IC packaging substrate

#### **Electronics product**

- TV / Laptop

- Smart phone

- Consumer products

#### VNA BASED S-PARAMETER FOR SIGNAL INTEGRITY ANALYSIS

COMPANY RESTRICTED

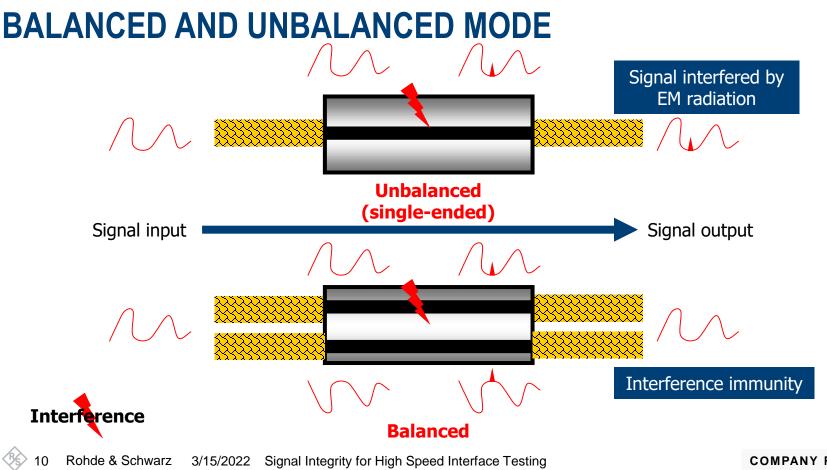

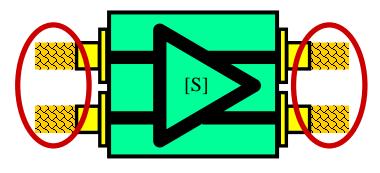

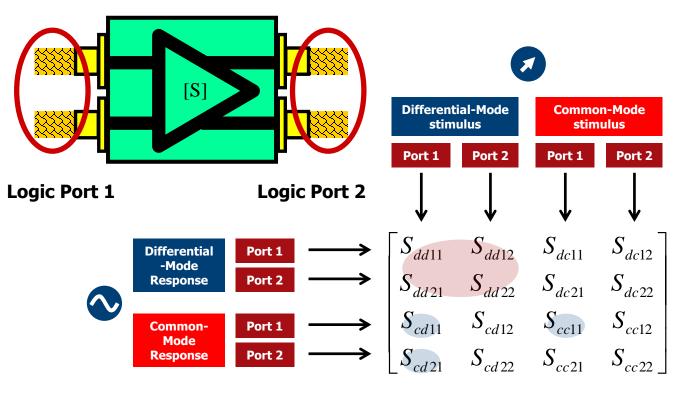

### **MIXED-MODE S-PARAMETER MATRIX**

Logic Port 1

Logic Port 2

x and y can be:

d (differential mode)

c (common mode)

1 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

#### **MIXED-MODE S-PARAMETER MATRIX**

#### HIGH-SPEED INTERFACE CHALLENGES AND TEST REQUIREMENTS

### **TIME VS. FREQUENCY FOR A SIGNAL**

**Ideally**

14 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

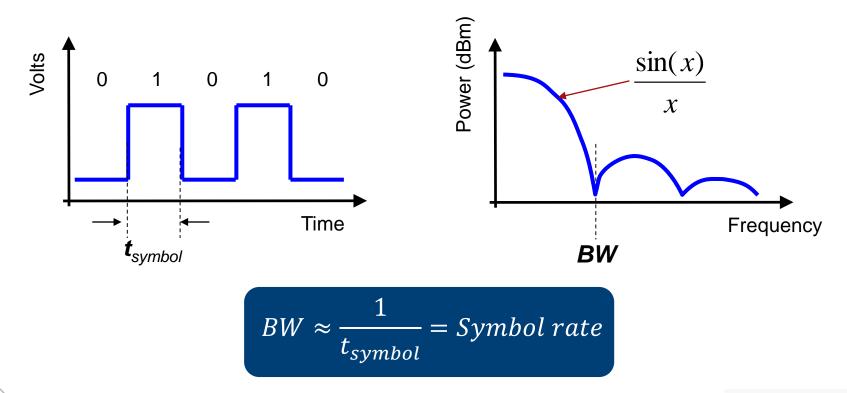

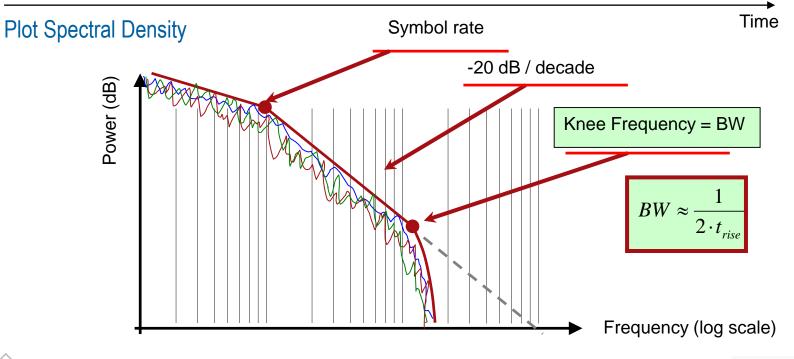

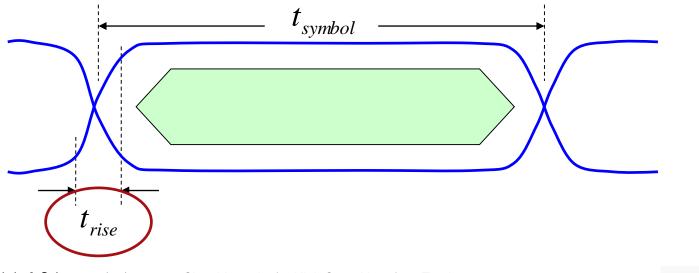

# WHAT IS THE REQUIRED BW?

#### **Actually**

# **REQUIRED BW CALCULATION**

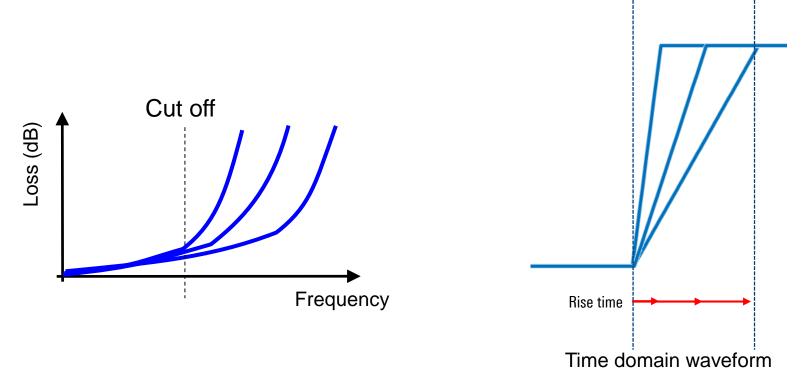

- ► Transmitter's Rise Time is specified as 50 ps

- Estimate the require bandwidth

$$BW \approx \frac{1}{2 \cdot t_{rise}} = \frac{1}{100 \, ps} = 10 GHz$$

16 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

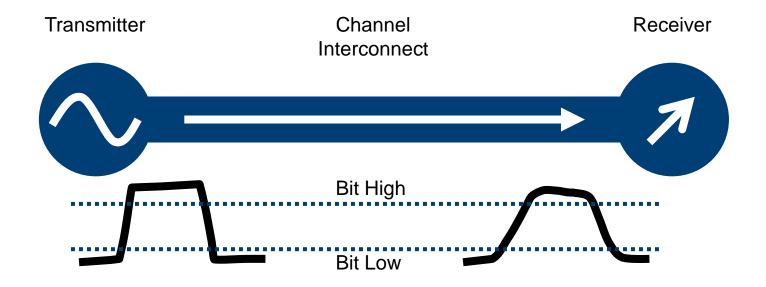

# SIGNAL TRANSMISSION

7 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

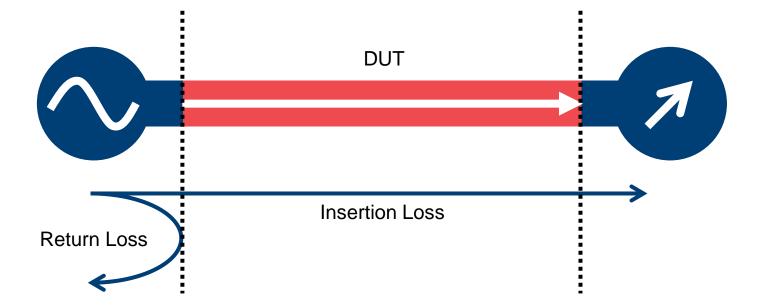

## SIGNAL INTEGRITY TEST REQUIREMENTS

# SIGNAL INTEGRITY TEST REQUIREMENTS

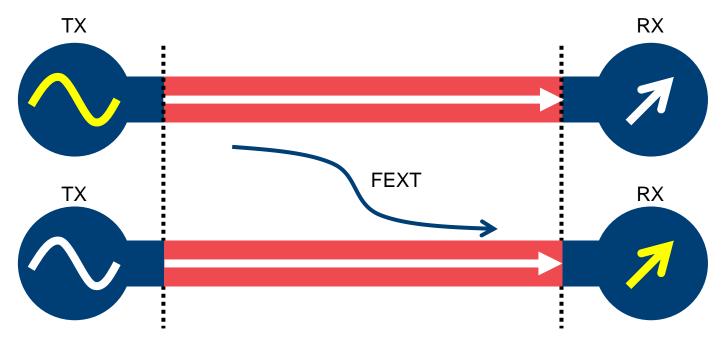

#### Far-End Crosstalk (FEXT)

9 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

# SIGNAL INTEGRITY TEST REQUIREMENTS

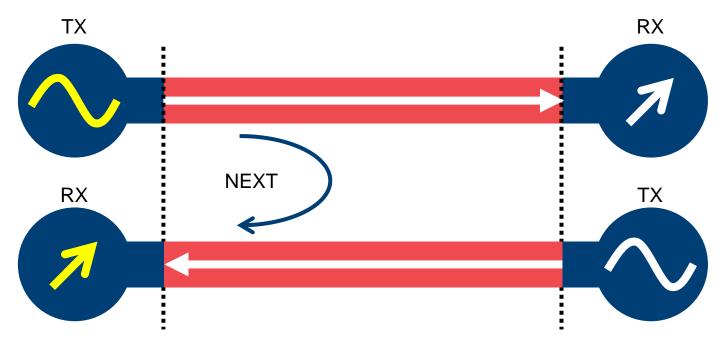

#### Near-End Crosstalk (NEXT)

20 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

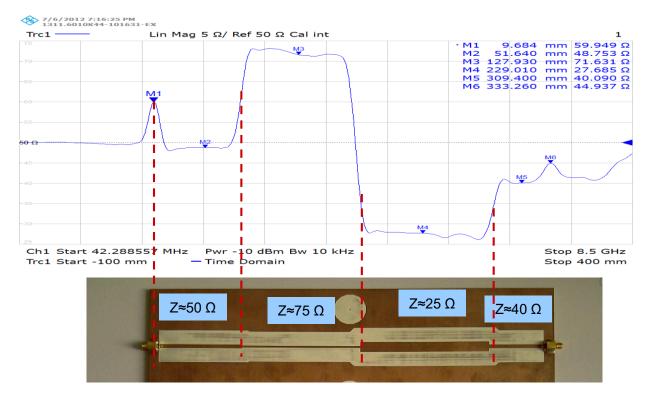

### **TDR IMPEDANCE MEASUREMENT**

## **TDT RISE TIME**

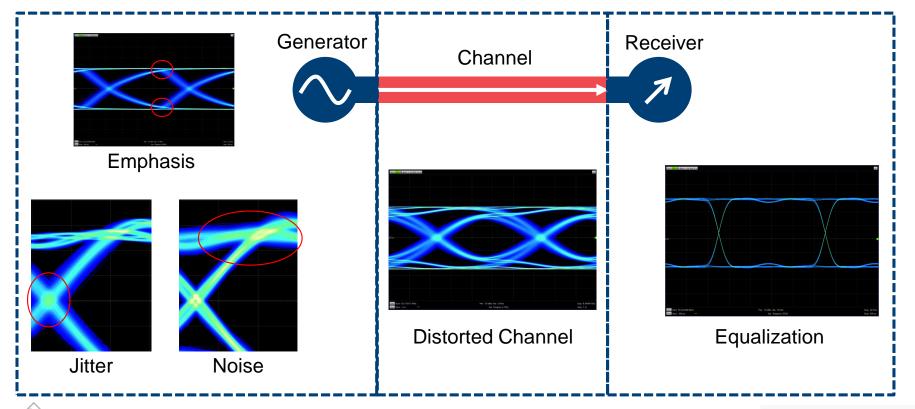

#### **EYE DIAGRAM**

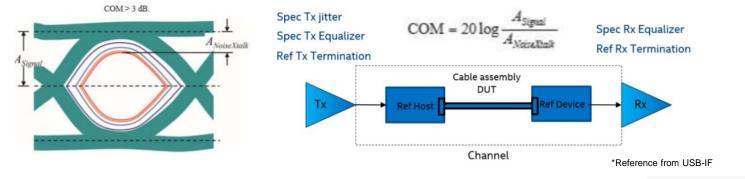

## **EFFECTIVE RETURN LOSS (ERL) AND CHANNEL OPERATION MARGIN (COM)**

- ► Effective Return Loss (ERL)

- Return loss with receiver EQ

- Transmitter noise

- Receiver frequency response

- Channel Operation Margin (COM)

- Insertion loss

- Isolation for FEXT and NEXT

- Integrated Crosstalk Noise (ICN)

- Effective voltage for power sum of NEXT and FEXT crosstalk

- Integrated Common-Mode Conversion Noise (ICMCN)

- Effective voltage for power sum of Scd21

#### ACCURATE MEASUREMENT WITH PROBES OR TEST FIXTURE

#### POSSIBLE SOLUTION: DIRECTLY PROBE THE DUT WITH RF MEASUREMENT PROBES

As an example using Packet Micro RF Probes. Required: S-Parameter of the RF probes

# **POSSIBLE SOLUTION: STANDARD FEATURE**

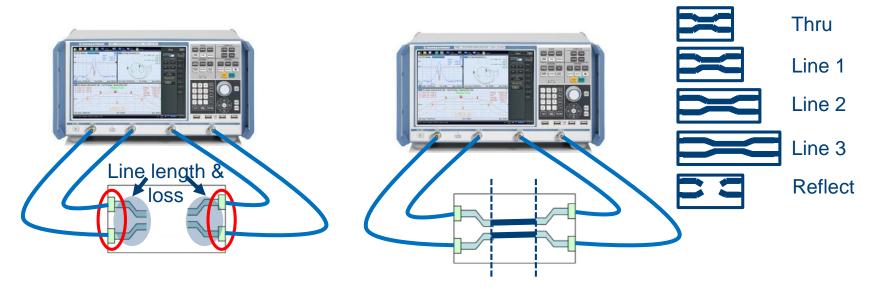

Auto Length and Loss

#### TRL Calibration

### **POSSIBLE SOLUTION: DE-EMEDDING SW ALGORITHMS**

Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

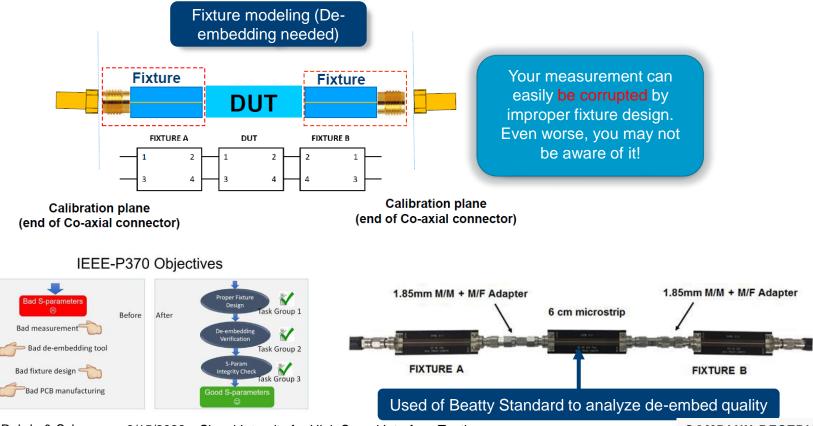

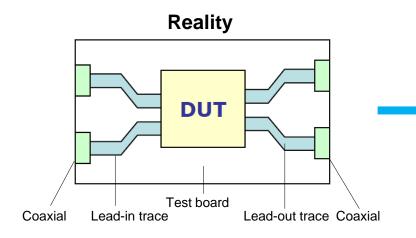

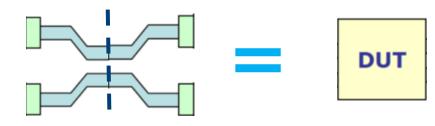

# **DE-EMBEDDING PRINCIPLE**

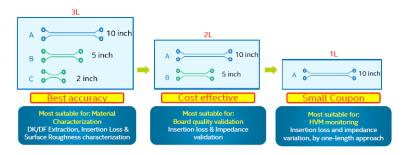

#### **Test Coupons**

- Test board + DUT

- Fixture with lead-in + lead-out structure and DUT on it

- ► Test coupons

- PCB with only lead-in + lead-out to form a through-like structure

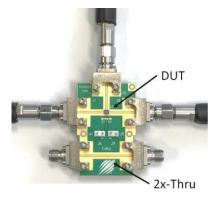

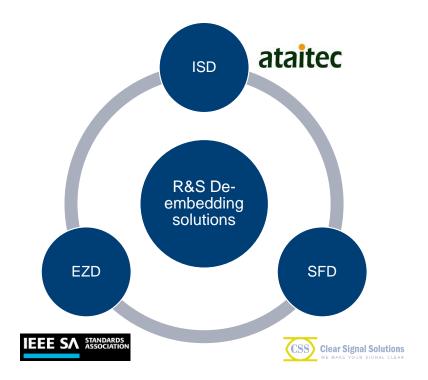

# **R&S VNA TEST FIXTURE DE-EMBEDDING SOLUTION**

- Available for R&S ZNA / R&S ZNB R&S ZNBT / R&S ZND VNA models

- Industry accepted SW algorithms

- IEEE P370 verified de-embedding tools: EZD, ISD, SFD

- PCB Characterization: Delta-L V4.0

- Easy to use

- One box solution

- Workflow GUI

- Full remote support

# DELTA-L GUI EXAMPLE SOLUTION WALKTHROUGH – OPTION ZNX-K231

- ▶ Press Offset Embed button, Delta-L calculation is a simple 3-step process:

- 1. Delta-L setup

- 2. Measurement

- 3. Algorithm results

► All of these steps can be operated via SCPI as well.

Delta-L V4.0 demo

#### FIXTURE MODELING DE-EMBEDDING TECHNIQUES R&S SOLUTION TEST FIXTURE DE-EMBEDDING

- Industry accepted SW algorithms

- ISD: In-Situ De-embedding

- SFD: Smart Fixture De-embedding

- EZD: Eazy De-embedding

| Test Coupon         | ISD | SFD | EZD |

|---------------------|-----|-----|-----|

| 2x Thru             | •   | •   | •   |

| 1x Open             | •   | •   |     |

| 1x Short            | •   | •   |     |

| 1x Open + 1 x Short | •   |     |     |

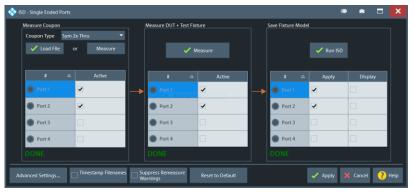

# **ISD GUI EXAMPLE**

- Press Offset Embed button, ISD calculation is a simple 3-step process:

- 1. Measure the 2x Thru

33

- 2. Measure the total structure: DUT + test fixture

- 3. Push the 'Run ISD' button and the VNA considers the algorithm results automatically

- ► All of these steps can be operated via SCPI as well.

Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

#### **ISD IMPEDANCE CORRECTION**

34 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

#### CONCLUSIONS

## CONCLUSIONS

- Most popular interfaces such as USB4, PCIe, and 400/800G Ethernet produces signal integrity issues due to higher data rate achieved and higher bandwidth required.

- Signal integrity analysis for high speed interface measurement items covers

- Frequency domain: return loss, insertion loss, NEXT, FEXT, mode conversion...

- Time domain: TDR impedance, TDT rise time, TDT skew...

- Signal domain: emphasis, jitter, noise, distorted channel, equalization, COM, ERL, ICN, ICMCN...

- R&S VNA offers de-embedding methods:

- General de-embedding tools: EZD, ISD, SFD

- PCB characterization: Delta-L V4.0

36 Rohde & Schwarz 3/15/2022 Signal Integrity for High Speed Interface Testing

# **THANKS FOR YOUR ATTENTION**

3/1**a5/12020** rity for High Speed Interface Testing